|

产品类别:教学实验箱 产品编号: 更新时间:2022/10/2 16:52:01 浏览次数:次 评论次数: |

|||||

| 产品详细说明 | |||||||||||||||||||||||||||||||

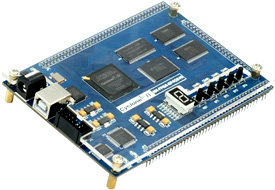

SZJ-JY806型 SOPC系统综合开发平台(实验箱) SZJ-JY806型SOPC系统综合开发实验箱,是一款基于Altera公司至新的CycloneIV 系列 EP4CE40高端实验开发平台。独有的GUI人机操作界面、采用系统底板+核心板+扩展板的灵活设计,并配备有20多种扩展模块供用户自行选择配置。适用于大中专职业院校教学实验与技能实训考核的理想教学实验箱。 一、开发平台特性: 1、GUI软件操作界面: 采用GUI人机操作界面,开机可显示温度、时间和设备信息等。整合开发平台上的硬件资源,点击子菜单中相关实验,液晶屏可与开发平台同步运行,提高学生动手兴趣和积极性,通过对设备各模块的检测和实验的演示,方便老师培训和设备检修。

2、模块化的灵活设计: 开发平台采用系统底板+核心板+扩展板的设计方法,通过选择不同的核心板和扩展板构成不同功能的开发平台。能至大限度的满足用户的性能需求。模块化的设计能使用户对系统设计有清晰的认识。 二、开发平台硬件资源: 1、NIOSII-EP4CE40 FPGA核心板 1)核心板采用10层高精度PCB设计,系统运行更加稳定、可靠。 2)主芯片采用Altera的CycloneIV系列级FPGA EP4CE40F23C8N,电路高达360万门。 3)FPGA配置芯片采用EPCS16,容量高达16MBIT,擦写次数高达上万次。 4)提供JTAG编程模式。 5)核心板板载USB-Blaster电缆;只需要一根USB线就可以对核心板进行程序下载。 6)一路50M高速、稳定的时钟源。 7)一路系统复位电路。 8)系统电源管理模块能够提供+5V、+3.3V、+2.5V、1.2V等多种不同电压的电源输出供系统使用。 提供两路SRAM,芯片采用IDT71V416-10P。容量高 9)达256K*32BIT。 10)一路FLASH 芯片采用AM29L128M。容量高过16M*8BIT。 11)一路16M*16BIT SDRAM。 12)系统提供四位通用的复位按键和四位通用的发光管和一个静态七段码管显示。 13)核心板提供与核心板其它资源不复用的190个以上的IO供用户二次开发使用。 2、EDA/SOPC系统板 1、标配800*600 16位TFT彩色LCD显示。用户可更换不同规格的显示屏和触摸屏。 2)1个模拟信号发生器模块,可提供频率、幅度均可调的正弦波、三角波、锯齿波、方波等信号波形。 3)1个数字时钟输出模块,可提供24M至1HZ的数字脉冲信号。 4)1个双道道10位高速并行ADC接口模块,速度高达40 Msps。 5)1个双道道10位高速并行DAC接口模块速度高达33 Msps。 6)1个串行A/D转换接口。 7)1个串行D/A转换接口。 8)1个VGA接口模块。 9)1个UART串行通迅模块。 10)1个USB Device设备接口。 11)1个USB Host主机接口。 12)1个Ethernet10M/100M高速接口模块。 13)SD卡接口模块 14)2个PS2接口模块,可以接键盘或鼠标。 15)1个I2C接口的E2PROM,型号为AT24C08N。 16)1个音频CODEC模块(立体声双通道输出)。 17)1个音频喇叭输出模块。 18)1个RTC实时时钟芯片,具有时钟掉电保护、电池在线式充电功能。 19)个拨动开关和12个按键开关输入 20)个发光LED显示。 21)1个八位七段码管显示模块。 22)16x16矩阵led点阵显示模块。 23)4X4矩阵键输入模块 24)1个电压控制的直流电机和1个四相的步进电机模块。 25)1个数字温度传感和1个霍尔传感器模块。 26)HH—EXT高速接口模块。 27)多路电源输出(均带过流、过压保护)。

三、示例实验: 1、EDA实验与电子设计竞赛实验内容: 1)简单的QUARTUSII实例设计 2)基于VHDL格雷码编码器的设计 3)含异步清零和使能的加法计数器 4)八位七段数码管显示电路的设计 5)数控分频器的设计 6)图形和VHDL混合输入的电路设计 7)步长可变的加减计数器的设计 8)四位并行乘法器的设计 9)设计四位全加器 10)可控脉冲发生器的设计 11)基本触发器的设计 12)矩阵键盘显示电路的设计 13)16*16点阵显示实验 14)直流电机的测速实验 15)步进电机驱动控制 16)PS2接口键盘显示实验 17)VGA彩条信号发生器的设计 18)用VHDL设计七人表决器 19)用VHDL设计四人抢答器 20)正负脉宽调制信号发生器设计 21)数字频率计的设计 22)多功能数字钟的设计 23)数字秒表的设计 24)、出租车计费器的设计 25)基于VHDL数码锁的设计 26)PS2鼠标编码设计 27)SPI串行AD/DA转换器的设计 28)DDS信号发生器的设计 29)序列检测器的设30)伪随机数发生器的设计 31)八位数据锁存器的设计 32)至高优先编码器的设计 33)解复用器的设计 34)带同步复位的状态机的设计 35)嵌入式逻辑分析仪的使用 36)SPI串口内核的实现 …… 2、NIOSII32位处理器示例实验 1)至简单NIOSII系统设计 2)带外部SRAM的NIOSII系统设计 3)Nor Flash编程实验 4)PIO外部中断按键开关实验 5)PIO输入-开关信号的读取实验 6)基于Timer IP核的定时器的设计 7)矩阵键盘与数码管显示实验 8)高速AD和高速DA实验 9)UART串口通迅实验 10)基于IIC的EEPROM读写实验 11)1-WIRE数字温度计的设计 12)串行AD/DA转换实验 13)SDRAM读写操作实验 14)彩色LCD液晶显示实验 15)触摸屏控制实验 16)RTC实时时钟实验 17)音频Code实验 18)USB枚举实验 19)PS/2键盘显示实验 20)PS/2鼠标控制实验 21)读SD卡实验 3、DSP Builder 设计应用示例实验 1)从DSP Builder到HDL——基于DSP Builder的信号发生器 2)从DSP Builder到SOPC Builder——软件控制的Chirp信号发生器 3)IP核在DSP Builder下的使用——以FFT核为例 4、综合开发实验 1)网络WEB控制实验 2)点阵显示屏的设计 3)直流电机闭环调速的设计 4)USB接口文本阅读器的设计 5)简易数字示波器设计 6)简易频谱分析仪设计 7)基于UART通信液晶显示实验 8)基于UART通信BMP图形显示实验 9)FAT32文件系统读SD卡实验 10)FAT32文件系统写SD卡实验 11)FAT32文件系统读写-拼音输入法的设计 12)彩色液晶原理与绘图应用实验 13)基于NIOSII贪食蛇游戏设计实验 14) 基于NIOSII计算器设计实验 15)在niosII上运行uC/OS系统 16)在niosII上运行uClinux系 四、产品配置:

注:使用本实验箱的配套仪器:电脑、示波器、万用表。

|

|||||||||||||||||||||||||||||||

客服1

客服1